Ch6 内存模型简介-存储设备

在本章中,我们将简介ROM和闪存这一类低速存储设备, 并研究用于在闪存中储存信息的浮栅二极管。 最后, 我们将对不同类型的低速存储设备进行简要介绍, 并探讨如何在Verilog中定义存储。

- 只读存储器

ROM和闪存 - 其他的低速存储设备: 磁盘和光盘

- 存储在

Verilog中的定义方式

1. 只读存储器 ROM 和闪存

1.1 只读存储器

只读存储器 ROM 的电路设计原理和随机存储器相近, 但成本更低. ROM 和 RAM 的主要差别在于: ROM 是 只读的非易失性存储器, 通常用于存储没有修改必要的核心操作系统程序, 固件或微码.

对于大部分的只读存储器而言, 它们承载的数据在工厂生产阶段即被写入, 并且这个过程是不可逆的. 只读存储器成本低廉, 常用于 ASIC (特殊应用集成电路). ROM 的访问界面和 SRAM 相似, 并且一些可被二次写入的 ROM 同样具有写入引脚:

随着技术的发展, 所谓的 “只读存储器” 类别中也出现了可在出厂后被一次性重编程或可被用户多次写入的产品, 称其为 PROM 或 EPROM/EEPROM.

-

PROM

全称为Programmable ROM, 是一种可在出厂后被一次性重编程的只读存储器. 数据在生产过程中并不会被烧录其中, 而是需要特殊的设备才能实现数据的烧录. 数据烧录过程中, 位于PROM内部用以标示二进制位的保险丝会根据所要烧录的数据内容而选择性熔断, 因而对其进行的数据烧录是不可逆的, 一旦数据在烧录过程中出现错误, 存储芯片只能被废弃. -

EPROM

全称为Erasable Programmable ROM, 使用浮栅阵列存储数据, 所存储的数据可通过紫外线照射而抹除, 并可以多次写入. 这类存储芯片常见于 $21$ 世纪早期的PC主板上用来存储BIOS数据, 现在已经极为罕见. -

EEPROM

全称为Electroinc Erasable Programmable ROM, 使用浮栅二极管阵列存储数据, 数据使用纯电路方式即可写入和抹除, 是最为常见的存储设备类别. 和随机存储器RAM不同,EEPROM在读取数据时的寻址时间相对写入数据所消耗的时间要长得多. 对于实现方式不同的EEPROM而言, 它所支持的数据抹除方式也有不同: 若某个EEPROM由多个容量较小的块组合而成, 那么在抹除数据时, 可以抹除的最小单位为块.

闪存, 包括 NAND, Solid State Drive 等均属于 EEPROM 类别. 相对 SRAM 或 DRAM, 它们的速度要低得多.

1.2 浮栅二极管

下面我们研究 浮栅二极管:

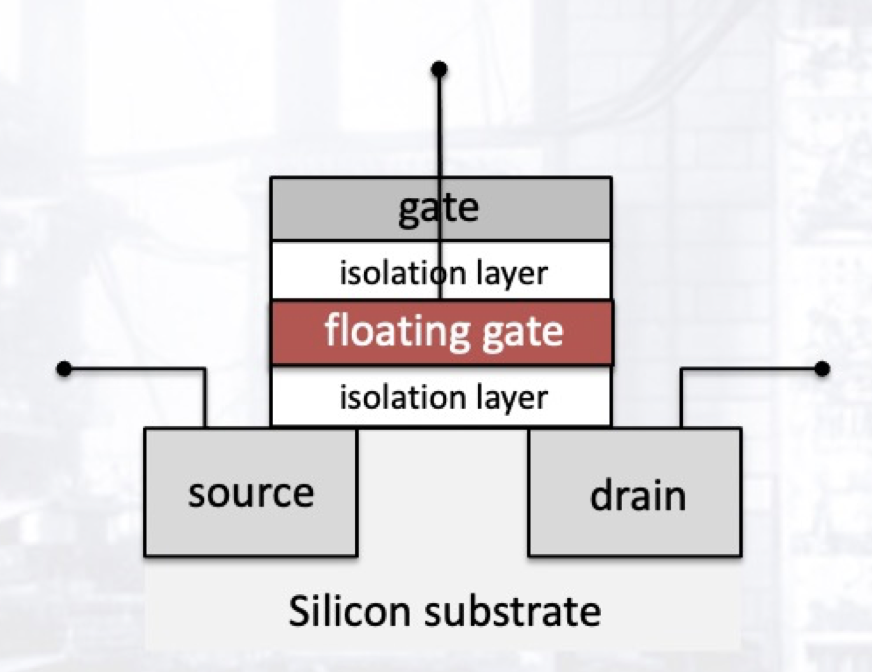

浮栅二极管 (Floating Gate transistor) 是 金属-氧化物半导体场效应二极管 (MOSFET) 的一个变体. MOSFET 有三个端子, 即栅极、源极和漏极. MOSFET 的名称来自其结构: 金属层位于非导电隔离层顶部,而该隔离层又在半导体层的上方. 该二极管用于控制源极和漏极之间的传导.

源极和漏极被一个半导体通道所分隔开. 当一个够大的电位差施于 MOSFET 的栅极与源极之间时, 电场会在氧化层下方的半导体表面形成感应电荷, 而这时反转通道(Inversion Channel)就会形成, 其极性与其漏极与源极相同. 通道形成后,MOSFET 即可让电流通过, 而依据施于栅极的电压值不同, 可由 MOSFET 的通道流过的电流大小亦会受其控制而改变.

-

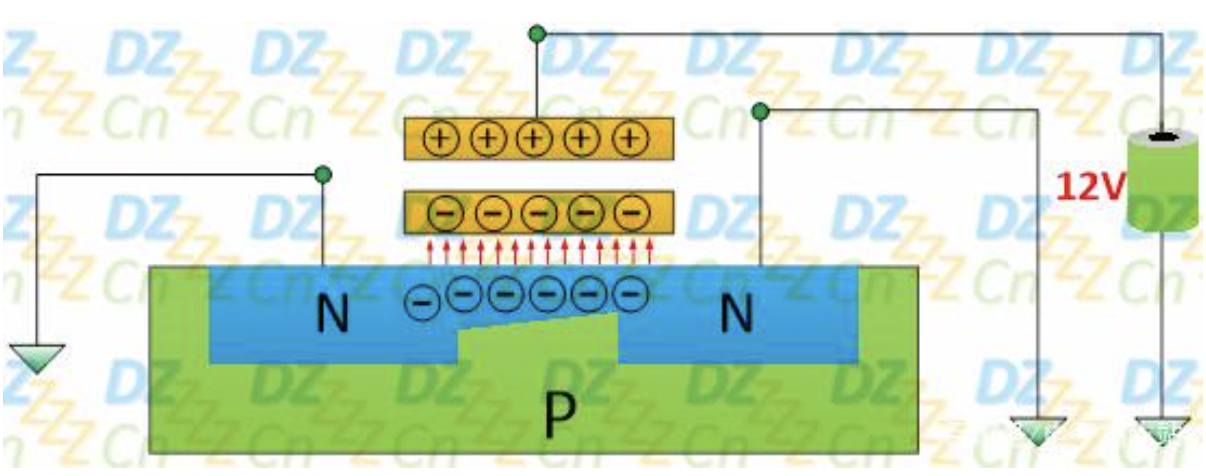

数据写入过程

在不对二极管的栅极施加电压时, 漏极与源极之间为开路. 要存储信息, 我们只需对栅极施加强电压并将漏极和源极接地. 这将导致在隔离层之下的栅极和源极之间形成传导通道. 电子将在这个区域聚集, 充能后突破隔离层到达浮栅门. 在上下两层隔离带的控制之下, 浮栅门中存储的电子即使在栅极施加的电压被撤除后也很难自由溢出.

-

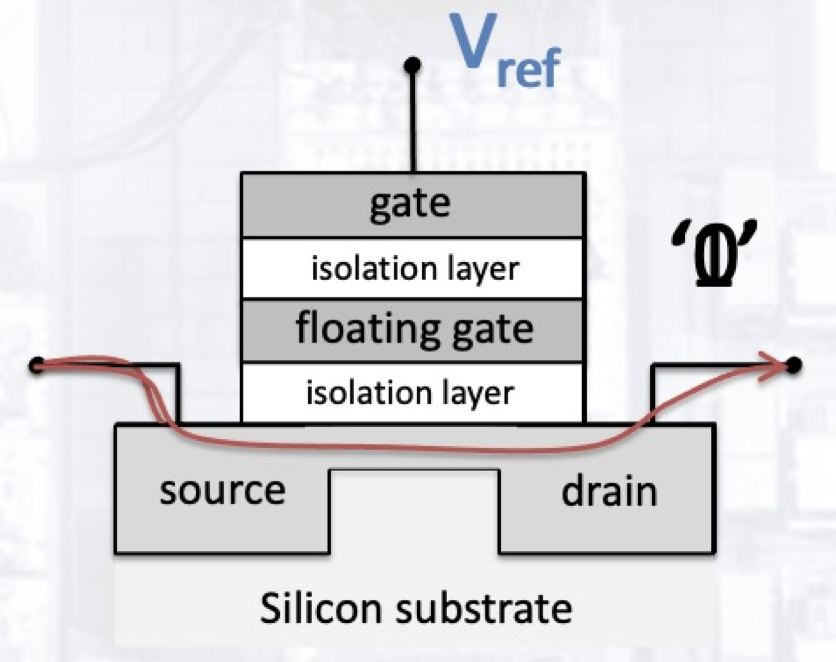

数据读取过程

当浮栅中注入或释放了电子时, 该二极管的导通阈值电压会发生改变. 因此, 只需要对栅极施加一个位于充/放电状态下的导通阈值电压之间的中间电平, 使得浮栅中存有电子的二极管无法导通而放电后的浮栅可以被导通. 这样, 通过检测该二极管的源极和漏极之间能否允许电流流过, 即可判断它处于何种状态之下.

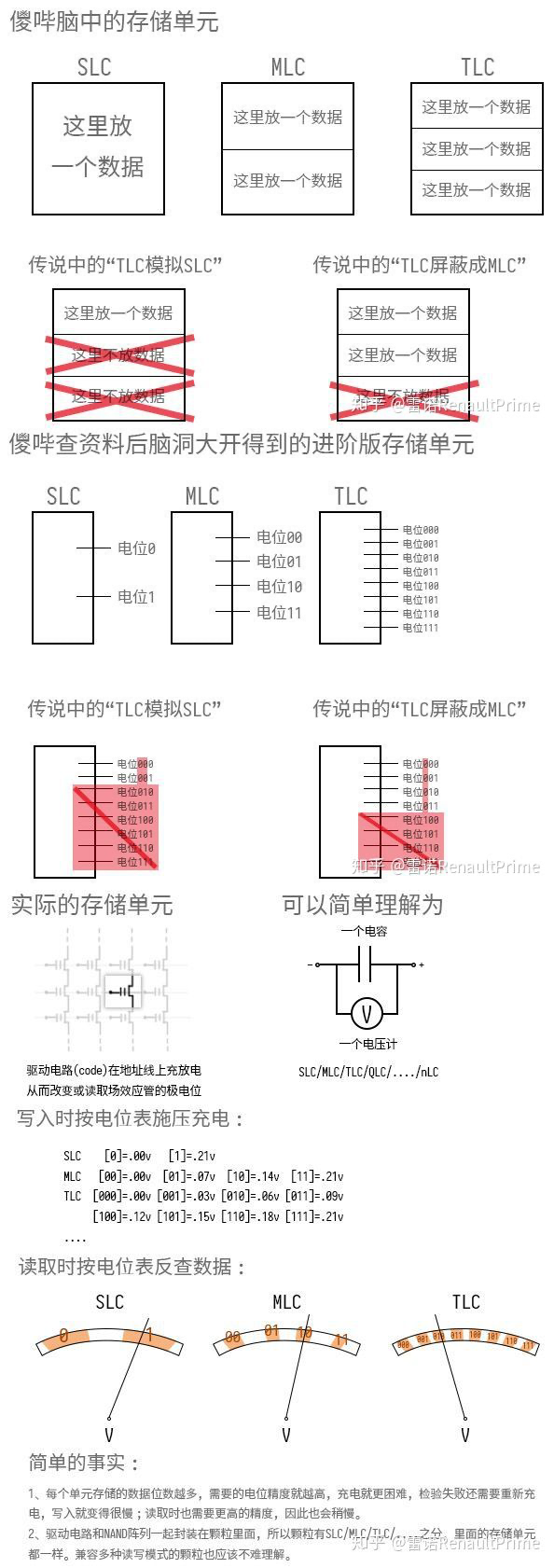

下面盗用源于知乎的一张小图对 SLC, MLC, TLC 进行傻瓜化介绍:

1.3 存储块

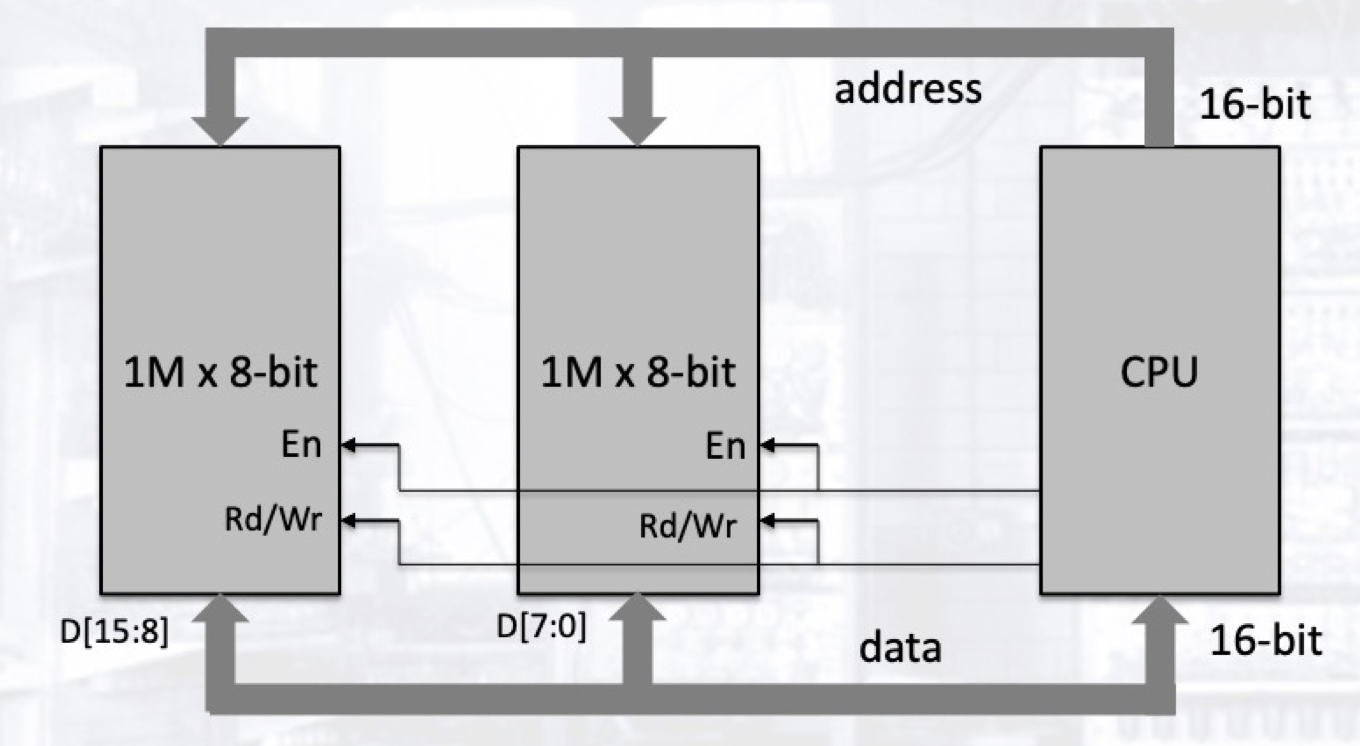

单片内存颗粒的存储容量和支持的数据位宽都是有限的. 通过将这些内存颗粒并行连接, 就可以满足更先进架构, 如 32 位或 64 位计算机的需要.

如下图所示: 我们将两个 $1$ MB, $8$ 位宽的存储块并行连接, 构成了一块 $1$MB, $16$ 位宽的存储. 两个子块共享相同的地址总线, 而作为输出的数据总线由两个子块的输出分别组合而成. 在这个结构中, 两个子块分别负责了较高位的 $8$ 位数据输出和较低位的输出. 这样的层级构造对处理器而言会被抽象为一个 $16$ 位宽的存储块. 如果我们需要更大的数据位宽, 可以用类似的方法对并联更多的存储块以满足需求.

除了并行连接多个位宽较小的子块实现更大的数据总线位宽以外, 我们还可以将它们串行连接以获取更大的存储深度 (即更大的存储容量).

2. 其他的低速存储设备: 磁盘和光盘

扩展阅读内容, 摸了(

3. 存储在 Verilog 中的定义方式

3.1 一般化定义

从抽象的角度来看, 存储和数组一样, 都可被视为一列数据, 并且可以对指定位置处的数据进行读取或者写入.

要在 Verilog 中定义一个数组, 我们只需要定义一个具有位宽和维度这两个属性的, 以寄存器为数据类型的变量:

1

2

reg [n-1:0] memory [0: 2^{m-1}]

; implement an array with 2^{m-1} locations, each n-bits wide

而要从所定义的存储器读取或写入某个位置的变量, 我们只需要提供一个地址:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

; READ:

address = &01C;

data_read = memory[address];

; the variable 'address' will contain the context from address '&01C'.

;----breaking line----

; WRITE:

address = &0F2;

data_to_write = &FFFF

memory[address] = data_to_write;

; the value '&FFFF' will be written to address '&0F2'

3.2 单端口 RAM

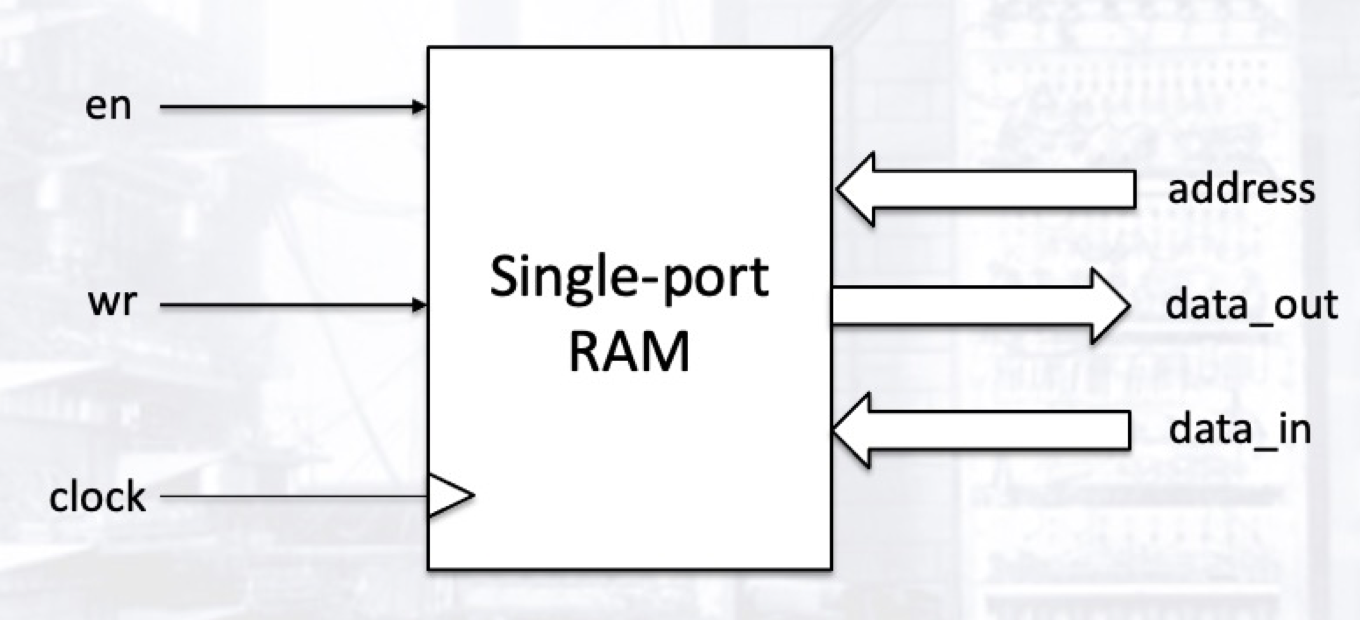

单端口 RAM 是一种只能串行执行读/写请求的存储设备. 它只受两个信号控制: 使能控制信号 en 和写入控制信号 wr, 另有一条数据总线用于传输要被写入或读取的数据.

在厘清其基本抽象结构后, 我们可以很容易地在 Verilog 中设计出单端口 RAM 这一时序电路:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

module single_port_ram (input wire en, wr

input wire clock;

input wire [15:0] data_in;

input wire [15:0] address;

output reg [15:0] data_out;)

reg [15:0] data_RAM [0, 65535];

always @ (posedge clock) ; synchronous circuit

if (en) ; only if enabled

if (wr)

data_RAM[address] <= data_in; ; perform mem write

else

data_out <= data_RAM[address]; ; perform mem read

endmodule

3.3 多端口 RAM

和单端口 RAM 相比, 多端口 RAM 有多条数据输入和输出总线, 并且设有多条控制信号以单独控制每一条总线, 这使得它可以并行读/写数据. 下面以双端口 RAM 为例:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

module dual_port_ram (input wire en1, en2, wr

input wire clock;

input wire [7:0] data_in;

input wire [15:0] address1, address2;

output reg [7:0] data_out1, data_out2;)

reg [7:0] data_RAM [0, 65535];

always @ (posedge clock) ; synchronous circuit

if (en1) ; only if enabled

if (wr)

data_RAM[address1] <= data_in; ; perform mem write

else

data_out1 <= data_RAM[address1]; ; perform mem read

always @ (posedge clock) ; synchronous circuit

if (en2) ; READONLY

data_out2 <= data_RAM[address2]; ; perform mem read

endmodule

双端口 RAM 通常被用作显存 (VRAM). 其特性使得在处理器将显示信息写入 VRAM 的同时, 用于输出图像的硬件电路可以同时从 VRAM 中读取信息.